您好,我是琳宇,欢迎来到我的个人网站。 Hi, I'm Linyu. Welcome to my personal site.

我在湖南大学,上海交通大学分别取得电子科学与技术工学学士和硕士学位, 目前是一名研究人员, 如果您是HR, 投资人,或是对我的文章或者项目感兴趣,欢迎联系我。 I received my B.S. and M.S. in ECE from the Hunan University and Shanghai Jiao Tong University. Currently I am a researcher. If you are HR, investor or interested in my projects, welcom to contact me.

1 AI for EDA

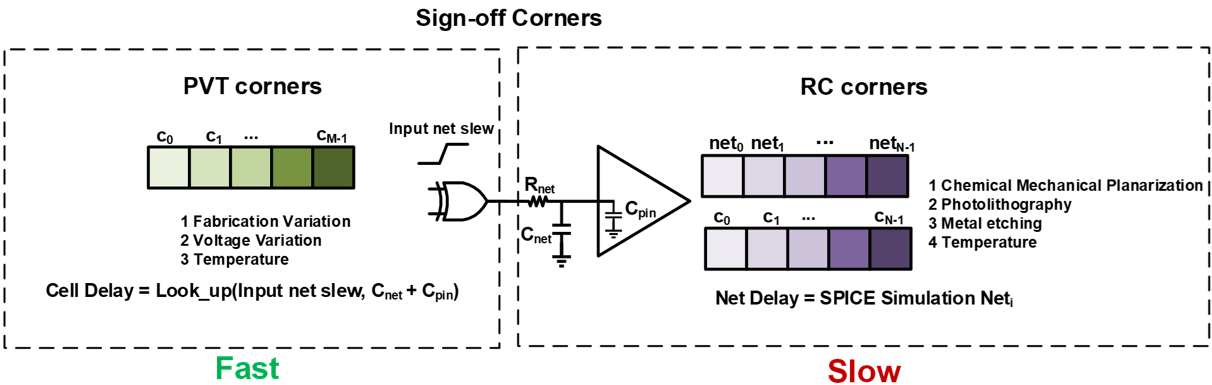

1.1 AI accelerates Multi-corner Wire Timing Signoff

Some of this project has been published in ICCAD24 and AICAS23.

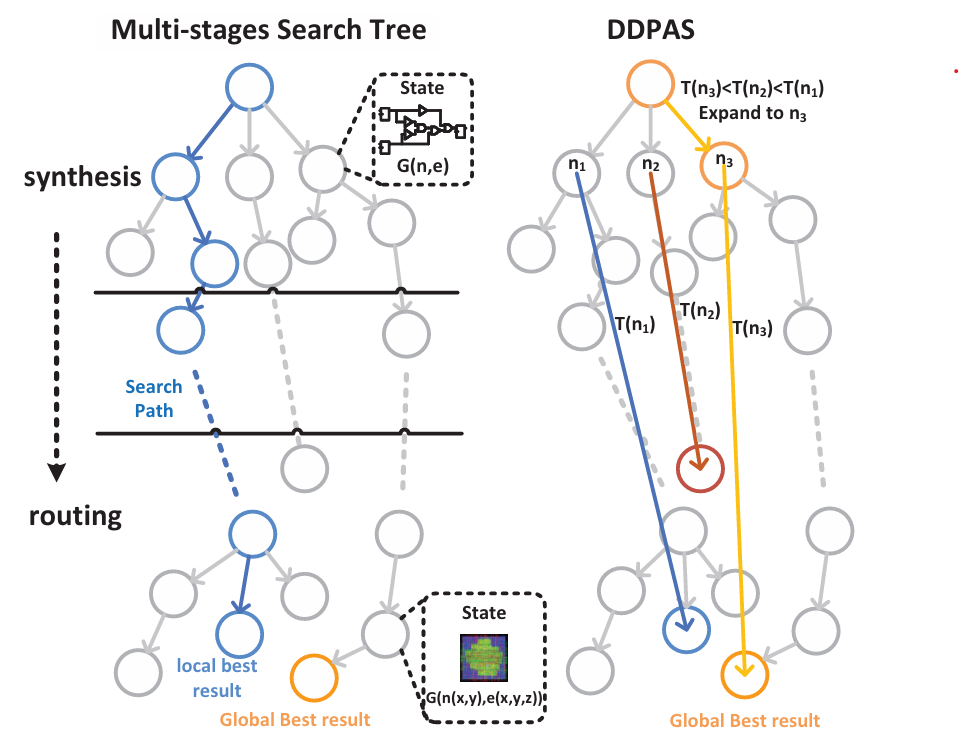

🔗 GitHub Code1.2 Physical-aware Logic Synthesis

Some of this project has been published in ICCD23.

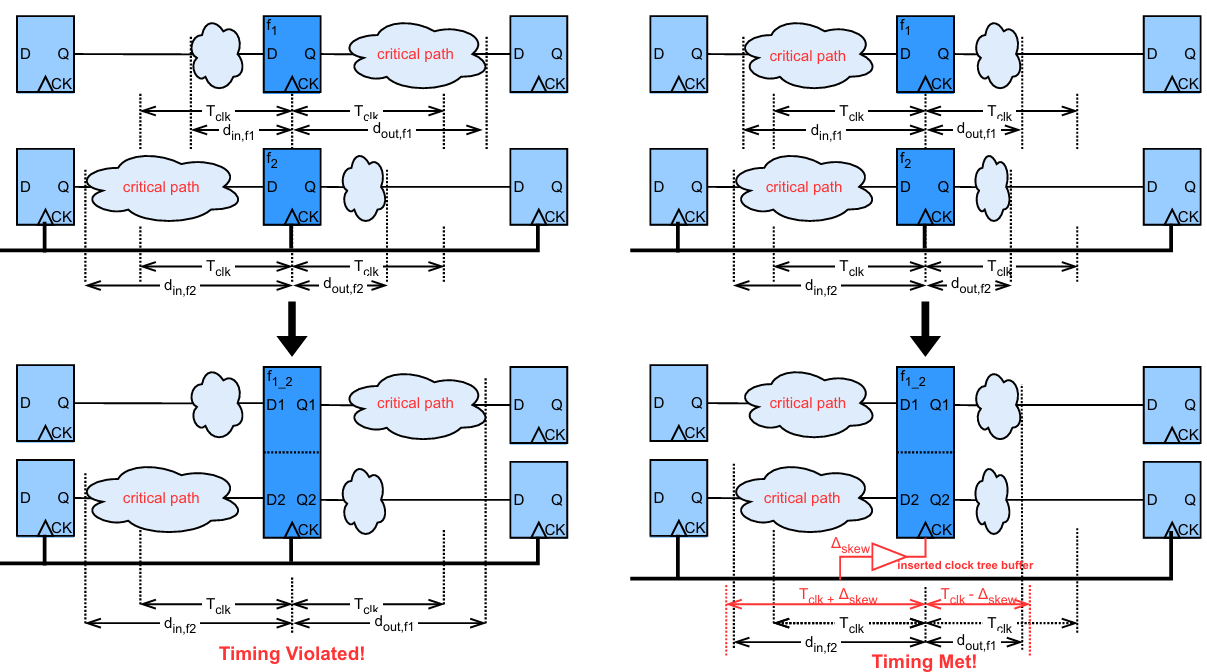

🔗 GitHub Code1.3 Multi-bitflip-flops clustering with wire timing prediction

Some of this project has been published in ASP-DAC25.

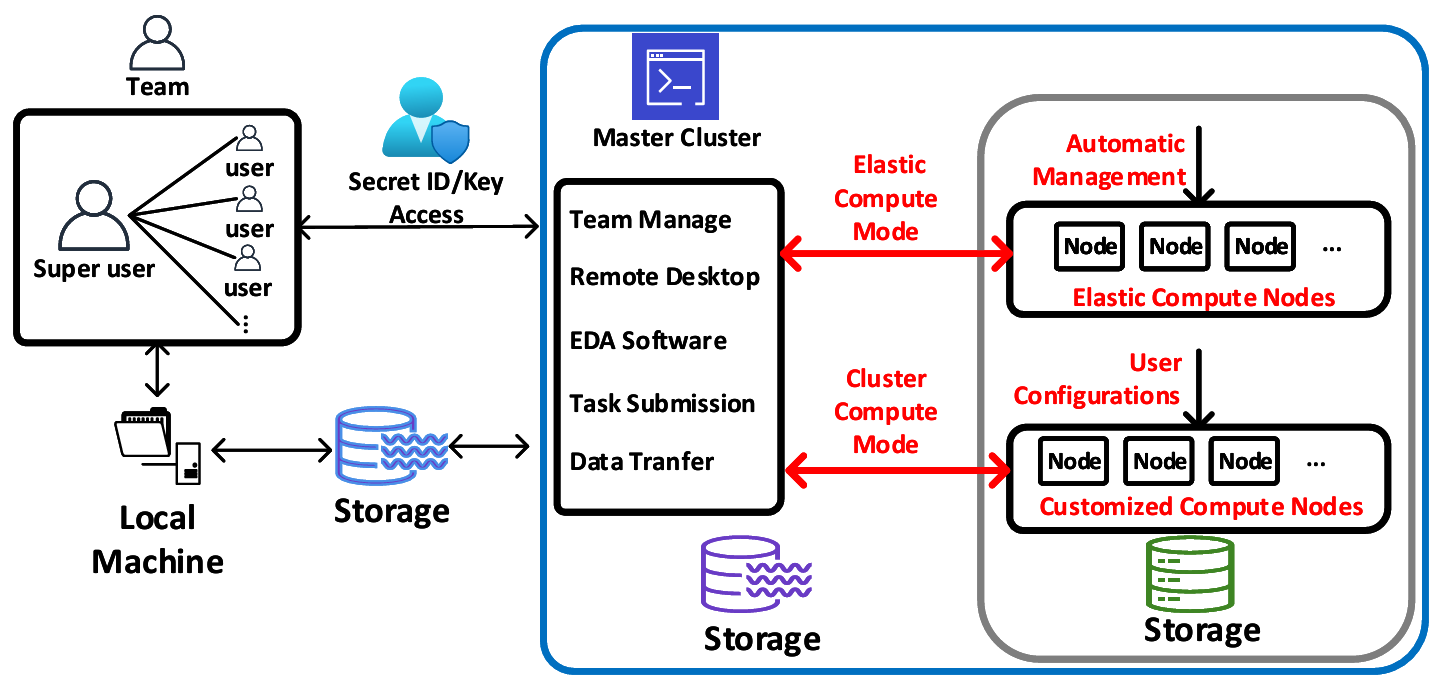

🔗 GitHub Code1.4 Elastic eda: Auto-scaling cloud resources for eda tasks via learning-based approaches

Some of this project has been published in ICCD24.

🔗 GitHub Code2. Advanced Design

2.1 TempestCache: Adaptive Cache Intelligence for the Modern Data Storm

This design is ongoing, now is on functional verification.

🔗 GitHub Code2.2 RISC-V CPU design with the fusion of front and back-end

2.3 RISC-V CPU design with the fusion of front and back-end

2.4 Physically aware AI accelerator SoC Design

3. Design Flow Dataset

3.1 CircuitS2L: Circuit Dataset Augmentation Framework by Generative Featuring and Supervised Labeling

Some of this project is submitted to ICCAD25.

🔗 GitHub Code3.2 7nm, 14nm, 28nm, 45nm EDA Design FLow Dataset

I have collected some dataset for AI4EDA tasks.

🔗 GitHub CodeRecent Publications

-

Extending silicon lifetime: A review of design

techniques for reliable integrated circuits

2025. arXiv: 2503.21165

Book -

AI-Enabled Electronic Circuit and System Design

Springer,2025

Book -

Learning-based Predictions for EDA Shift-left Paradigm

2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025

Poster -

Revisit mbff: Efficient early-stage multi-bit flip-flops clustering with physical and timing awareness

2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025

Paper -

One-for-all: An unified learning-based framework for efficient cross-corner timing signoff

2024 IEEE/ACM International Conference on Computer Aided Design (ICCAD), 2024

Paper , Slide -

Elastic eda: Auto-scaling cloud resources for eda tasks via learning-based approaches

2024 IEEE 42st International Conference on Computer Design (ICCD), 2024

Paper -

Integration of shift-left updates into logic synthesis and macro placement

Conference of Science and Technology for Integrated Circuits (CSTIC), 2024

Paper -

Delay-driven physically-aware logic synthesis with informed search

IEEE 41st International Conference on Computer Design (ICCD), 2023

Paper Code -

Rc-gnn: Fast and accurate signoff wire delay estimation with customized graph neural networks

IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2023

Paper -

Delay-driven physical-aware logic synthesis with reinforcement learning

2023 CCF 4th Integrated Circuit Design and Automation Conference (CCF-DAC), 2023

Paper -

A Promising Way of Energy Harvesting for Implantable Medical Devices – Thermoelectric Generator (TEG)

International Conference on Smart City and Green Energy (ICSCGE), 2021

Paper

Patent

-

Signoff-level timing prediction methods and systems across process corners

ZL202311787034.5

Link

Contact

📧 linyuzhu@sjtu.edu.cn | 💻 GitHub: Linyu-Zhu